High sampling rate/high resolution, accurate acquisition of dynamic signals

According to Nyquist sampling theorem, for dynamic signal acquisition, at least signal frequency 2x The above sampling rate can basically restore the frequency and amplitude characteristics of this signal. However, under the current data acquisition technology, twice the sampling frequency is far from meeting the test requirements. In many cases, it is recommended to use a sampling rate of 10 times or higher. The reasons are as follows:

① Higher sampling rate can better restore the signal time domain waveform, especially for dynamic vibration signals, shock signals, etc.

② With more sampling points per unit time, the number of data points in the FFT window can be increased, thus improving the spectral resolution of FFT and obtaining higher frequency domain accuracy.

Technical foresight - oversampling

Dewei Chuang TRION3 -The 18xx Multi board adopts a unique oversampling technology. The purpose of this design is to further increase the effective bits of AD on the premise of ensuring high sampling and high bandwidth, so as to obtain signal accuracy, signal to noise ratio and dynamic range. Theoretically, when the oversampling frequency processing is reduced to a lower sampling rate, 0.5 bit resolution will be increased for every half reduction of the sampling frequency. Therefore, DVC can maintain high precision, signal to noise ratio, dynamic range and other test performance while maintaining high sampling.

No phase difference in signal synchronization and consistent time series signal

For testing, the time domain accuracy and frequency domain accuracy of the test signal are very important preconditions. When the number of test channels is ≥ 2, the synchronization between test signals is a very important indicator due to the synchronization difference between different AD clock oscillators and equipment. For example, the following test requirements have high requirements for signal synchronization:

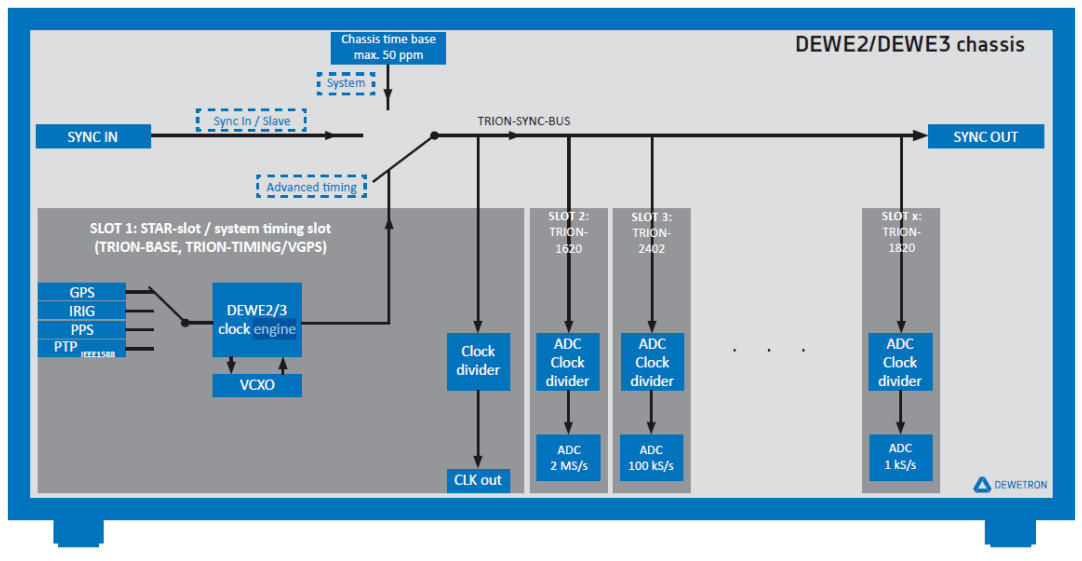

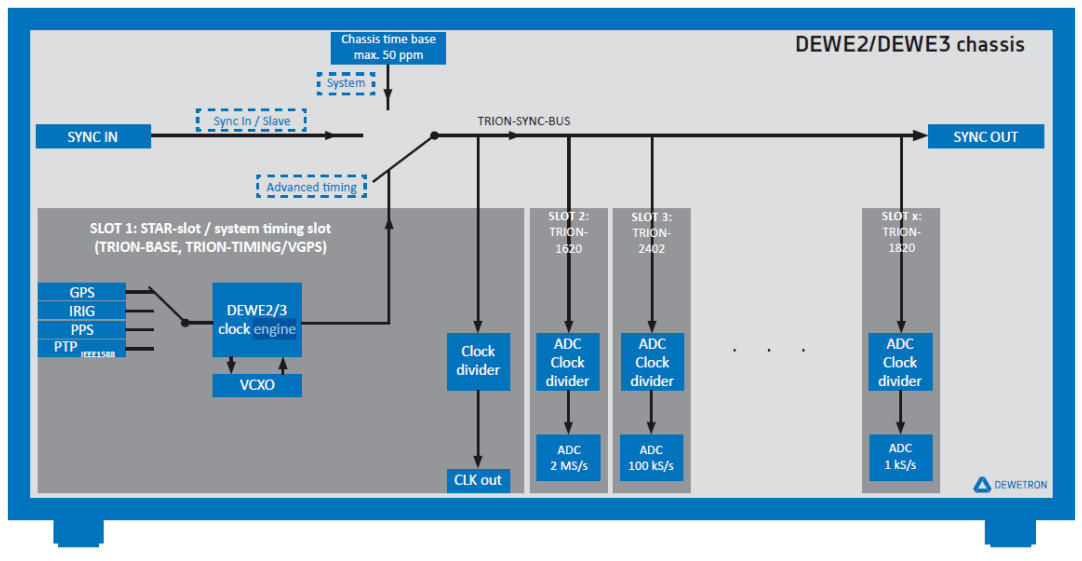

① Multi equipment networking large system requires unified time system signal (such as ignition), which must ensure clock synchronization of different equipment and minimum phase difference between channels;

② It is necessary to test and analyze the correlation/correlation between different channels, such as transfer function, frequency response, correlation/coherence, etc. It is necessary to ensure that there is no phase delay between channels.

③ For power test, the phase difference of current/voltage channel will directly affect the phase angle Phi, and then affect the power accuracy.

PXI/E clock bus advantages:

① Parallel clock bus, the phase delay between channels is as low as 10ns;

② The synchronization signals between different chassis are directly connected through the SYNC network cable, and the synchronization accuracy is better than 60ns;

③ Clock engine conversion, which can access external clocks such as IRIG/GPS/1558, and introduce PXI/E bus clock.